Available online at www.elixirpublishers.com (Elixir International Journal)

**Power Electronics Engineering**

Elixir Power Elec. Engg. 57 (2013) 14071-14072

# Simulation of Three-Phase Inverter Using Minimum Number of Controlled Switches

D. A. Kulkarni<sup>1</sup>, T. D. Dongale<sup>2</sup> and M. D. Uplane<sup>1-2</sup> <sup>1</sup>Department of Electronics, Shivaji University, Kolhapur. <sup>2</sup>School of Nanoscience and Technology, Shivaji University, Kolhapur.

## ARTICLE INFO

Article history: Received: 5 February 2013; Received in revised form: 17 March 2013; Accepted: 3 April 2013;

## Keywor ds

Inverter, Four Controlled Switches, PSIM, VFD (Variable Frequency Drive), IM (Induction Motor).

## ABSTRACT

Reduction in the number of component is a live problem in the domain of power electronics, as it is directly leads to reliability implication. Further reduction in active switches in the inverter topology is also beneficial for the cost factor point of view. In view of this, the present paper reports a novel inverter topology based on only four active switches as against the six switches topology widely reported in the literature. The said design is verified using PSIM software. The result shows good resemblance between our proposed four switches topology and conventional six switches topology.

© 2013Elixir All rights reserved.

## Introduction

The penetration of variable frequency drive into consumable market leads to efficient and cost effective new breed of variable frequency drives. In the view of this scenario the soft switching inverter topology are evolving [1]. The application domain of VFD in industrial sector pushes to its new technology discoveries. The application such as conveyors, machine tools, centrifugal machines, presses, elevators, and packaging equipment require the efficient and cost effective VFDs for their sustainability. The reduction in device count in the mainstream VFDs topology is the main challenges in front of researchers and engineers. The lot of work is carried out in the area of minimum device count [2-6]. The reduced controlled switches and freewheeling diode count from mainstream VSI topology further leads to cost effective products. The combination of increased performance and lower initial cost will allow for further penetration of adjustable speed drives into the consumer market. [5]

The research regarding with lees device count is studied and successfully implemented by many research group. The Frede Blaabjerg, et al proposed an adaptive space vector modulation (SVM) approach to compensate the dc-link voltage ripple in an inverter topology [1]. Similar work was carried out by Ching-Tsai Pan et al for a low cost voltage-fed current controlled inverter for induction motor drives [2], Heinz W. Van Der Broeck et al investigate the three-phase induction machine drive with a component minimized voltage-fed inverter under different control options [3]. J. F. Eastham et al reported the various power inverter topologies [4] and Brian A. Welchko and Thomas A. Lipo [5] reported a novel current source control method for a three-phase induction machine.

The present's paper reports the simulative approach for variable frequency drive using PSIM software. The reported simulative inverter design only uses four switches, which is different from conventional inverter topology. The organization of paper as follows, the section I is focused on introduction of proposed topology and relevant work for VSI topologies. Section II describes the actual method of simulation of proposed topology and finally the section III and IV describes the result and discussion respectively.

### Proposed Four Switch Inverter Topology

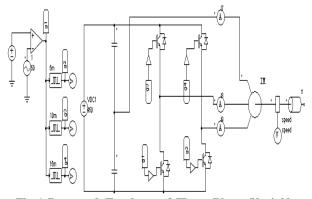

The simulation of four switch inverter was performed using PSIM (*Power SIMulator*) software. The fig.1 presents the proposed topology of three phase variable frequency drive (VFD) using only four controlled switches. In this simulation the IGBT's are used as controlled switches. The sinusoidal PWM technique was used for controlling the four switches. At given instant the two phases were conduct and each phase conducts for 240° of a cycle. For the simulations, the induction motor was connected as a load and the inverter is considered to be built by ideal switches. The output voltage of inverter is an addition of two leg switches and the dc-link voltages [1]. The actual simulative implementation is shown in fig.1 and the gating sequence of this proposed technique is shown in table I.

Table I. The Gating Sequence of Proposed Topology

| Switches on at Given Phases |     |

|-----------------------------|-----|

| V9                          | V10 |

| V9                          | V11 |

| V12                         | V10 |

| V12                         | V11 |

### Results

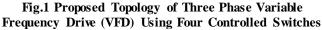

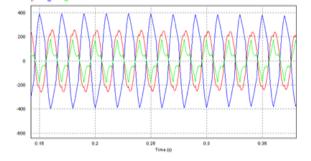

In order to investigate the proposed control method, simulations were performed using PSIM (*Power SIMulator*) software. The result shows good similitude between proposed inverter topology and conventional six switches inverter topology. The fig. 3 shows the phase current waveform of three phases as  $I_A$ ,  $I_B$ ,  $I_C$  respectively. The current waveform is unsatisfactory compared to conventional three phase current waveform. Fig. 4 presents the relationship between speed and current distribution during motor startup. The fig. 4 also shows the large settling time of induction motor for startup but it is quite satisfactory for such low cost VSI topology.

Fig. 4 Simulated Waveforms for Induction Machine Drive System during Motor Startup

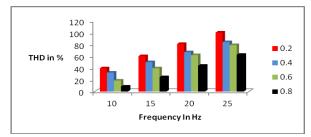

Fig. 5. Total Harmonic Distortion (THD) of Proposed Inverter Topology

The total harmonic distortion factor (THD) is presented in Table II and fig.5. The total harmonic distortion factor (THD) can be used as an optimization factor for VSI inverter in general. The THD is higher at the 0.2 modulation index and it is increases as frequency increases. The distorted output of the present topology is due to the harmonic and sub-harmonics [7-9].

#### Discussion

The present paper demonstrates the simulative approach for VFD with four controlled switches. The present simulation has good agreement in conventional VFD characteristics and proposed VFD characteristics. The total harmonic distortion (THD) problem present in the proposed topology but it can be overcome by advanced strategies such as adaptive space vector modulation (SVM) and improvement in DC link capacitor.

### References

[1] M. R. Amini and H. Farzanehfard, "Novel family of PWM soft-single-switched dc-dc converters with coupled inductors," IEEE Trans. Ind. Electron., vol. 56, no. 6, pp. 2108–2114, Jun. 2009.

[2] Frede Blaabjerg, Dorin O. Neacsu, John K. Pedersen, Adaptive SVM to Compensate DC-Link Voltage Ripple for Four-Switch Three-Phase Voltage-Source Inverters, IEEE Transactions On Power Electronics, VOL. 14, NO. 4, July 1999 [3] Ching-Tsai Pan, Tsung-Cheng Chen, Chen-Ming Hung,"A Low Cost Voltage-Fed Current Controlled Inverter for Induction Motor Drives," IEEE International Symposium on Industrial Electronics, pp. 434-9, 1993

[4] Heinz W. Van Der Broeck, J.D. Van Wyk, "A Comparative Investigation of a Three-Phase Induction Machine Drive with a Component Minimized Voltage-Fed Inverter Under Different Control Options," IEEE Transactions on Industrial Applications, Vol. IA-20, No. 2, March/April 1984, pp. 309-320

[5] J. F. Eastham, A. R. Daniels, and R. T. Lipcynski, "A novel power inverter configuration," in Proc. IAS'80, vol. II, pp. 748–751

[6] Brian A. Welchko and Thomas A. Lipo, A Novel Variable Frequency Three-Phase Induction Motor Drive System Using Only Three Controlled Switches, IEEE Industry Applications Society Annual Meeting Rome, Italy. October 8 -12, 2000, Paper Number 26.4, pp. 1-6

[7] F. Blaabjerg, S. Freysson, H. H. Hansen, and S. Hansen, "A new optimized space vector modulation strategy for a component minimized voltage source inverter," in *Proc. APEC 95*, vol. 2, pp. 577–585.

[8] G. T. Kim and T. A. Lipo, "VSI-PWM rectifier/inverter system with a reduced switch count," *IEEE Trans. Ind. Applicat.*, vol. 32, pp. 1331–1337, Nov./Dec. 1996.

[9] J. He and N. Mohanc, "Parallel resonant dc-link circuit—A novel zero switching loss topology with minimum voltage stresses," IEEE Trans. Power Electron., vol. 6, no. 4, pp. 687–694, Oct. 1991.