Iteeshree et al./ Elixir Image Processing 64 (2013) 19318-19323

Available online at www.elixirpublishers.com (Elixir International Journal)

Elixir Image Processing 64 (2013) 19318-19323

# Detection of Brain Tumor of Fetus Edge –Detection on MR Images and Implementation on FPGA

Iteeshree\* and Ashish Sharma

Department of Electronics, Banasthali University, Rajasthan, India.

### **ARTICLE INFO**

Article history: Received: 20 September 2013; Received in revised form: 3 November 2013; Accepted: 11 November 2013;

### ABSTRACT

This paper presents a proposal of detection of brain tumor of fetus through its MRI image during 25-27 week of pregnancy. This detection is based on edge detection technique and its implementation on FPGA. For FPGA implementation use MATLAB/SIMULINK graphical user interface with Xilinx System Generator which is the integrated design environment for FPGA within ISE11.3 design suit.

© 2013 Elixir All rights reserved

Keywords

Xilinx system generator; MRI; Edge-Detection; MATAB/SIMULINK.

### Introduction

Digital image processing has found many remedies for medical area. Different-different image modalities help in making pre-surgery decision. One of the greatest imaging modality is MRI. MRI stands for magnetic resonance imaging. This is a non invasive method of imaging .This is a spectroscopic imaging technique used to produce an image of inside human body working on a principle of nuclear magnetic resonance and obtain microscopic chemical and physical data about molecule.MRI gives a very clear picture of human internal body. MRI is very effective in brain injury cases; it gives clear picture of brain parts. Even a MRI can take of fetus brain during pregnancy period or if a fetus is suffering from tumor its detection is possible in that period too. The technique used for detection of brain tumor is edge detection.. Edges are essential feature of an image mainly used for detection purpose. Edge detection is a method of Segmentation. Segmentation is process a reducing an image into region that corresponds to specific structure unit.

Real time image processing is not satisfied by software implementation on a computer, a dedicated hardware needed to fulfill this real time requirement. Image and video processing application need more computational power for this .It can be implemented on ASIC or FPGA. The advantage of FPGA is high reprogram ability, parallism, flexibility, computational power prove that FPGA implementation is better choice than DSP or ASIC [2].FPGA using HDL is time consuming process and more complicated for large system design .This situation has been changing over with high level language programming tool such as Hardel C, Accsel DSP, Xilinx system generator. XSG is high level software tool that enable that uses of MATLAB\SIMULINK environment [2].

### **Modelling of Edge-Detection**

Edge detection is very basic research field in process of image analysis and measurement, the latter must rely on processing the information it provides and edge extraction directly affects the follow-up to the accuracy and ease of handling. The edge of the image is a set of pixels which a spatial image intensity or brightness of the direction of mutation or mutation carriers degree. It is a vector which includes magnitude and direction, in the image it shows as the mutation of gray scale. Edge detection is to detect non continuity of a gray image of and to determine their exact position in the image [4].

Edge detection is the method of segmentation. Segmentation is the main principle of working process; Segmentation is the process of reducing image to region that corresponds to structure unit imaging purpose, segmentation used to extract specific organ. Segmentation may divide image into anatomic, pathological, systemic of functional region. There is various method of segmentation.

- 1. Threshold-a)Global b)local

- 2. Edge detection

- 3. Region Growing

- 4. Parametric

- 5. Texture threshold

- 6. Multi spatial technique

In this paper simple method to perform threshold segmentation, simply generate MASK image based on selected threshold. Edges are used for scene interpretation; define the boundary for subsequent segmentation process. Image brightness characterized by positive  $x_p$  and orientation  $\square$  of brightness variation. Two problems comes in this-

1. Estimating edgels (edgels are edge element)

2. Grouping edgels in to edges

Edge detection-Edges are significantly local changes of intensity in an image. Firstly search for local maxima in the direction normal to local edge and then done non maximum suppression for searching local maxima by discrete sampling grid.

The goal is to define threshold for  $\Box I/\Box x$  and  $\Box I/\Box y$  taking in account the CNR. There are many filter weight kernel that applied in spatial domain.

## I<sup>st</sup> order Derivative filter

1. Robert

Sobel

Prewitt

<u>II<sup>nd</sup> order Derivative filter</u>

1. Laplacian of Gaussian

2. Laplacian

3. Difference of Gaussian

**Optimal filter**

#### Canny

These kernel are design to use maximally to edes running vertically and horizonatally relative to the pixel grid. The gradient magnitude given by Eq.1

| G  =  Gx  +  Gy                         | (1) |

|-----------------------------------------|-----|

| The gradient direction given by Eq.2    |     |

| - · · · · · · · · · · · · · · · · · · · | (2) |

## $[\tan^{-1}(\Box] \stackrel{<}{\xrightarrow{}})$

### Principle of Working

In medical imaging it is useful to extract different part of organ i.e. vascular structure or tissue type. Extracted image may have pixel value of original image or binary value. Edges are known as significant local variation in image brightness and contrast characterized by position and orientation of brightness value. Edges can be model according to their intensity profile. Edge detection defines edges of segmented portion. There are many derivative spatial domain filter weight kernel can be oriented horizontal, vertical, and then compute the response of each kernel. Larger the gradient kernel will give the less noisy more sharp image. Software used for this is and MATLAB/SIMULINK which works in graphical user interface of XILINX SYSTEM GENERATOR. SIMULINK is a graphical extension of MATLAB for modeling and simulation of system. SIMULINK are drawn on screen as block diagram.

The entire operation of edge detection proposed using Simulink and Xilinx blocks goes through 3 phases

- Image pre-processing block-set

- Edge detection block-set

- Image post-processing block-set

- Whole implementation

Pre-processed image

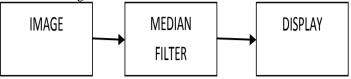

Image preprocessing block- In image preprocessing block image gets filtered by the median filter. Filter is necessary before processing because it reduces noise coming with the image and results become more accurate. In other way the filter when applied to a region with relatively constant intensity will respond by smoothing and shut down when applied to region with line or edges.

Figure-1 Pre-processing block-set

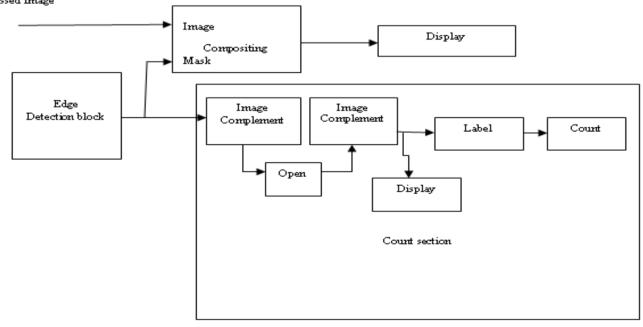

Edge-detection block-set- Implementation of the entire edge detection block-set with algorithms Sobel, Canny, Prewitt, Robert and Threshold as shown in Figure 2. If there is more that 1 tumor present in brain than count section will count the number of tumor present in brain.

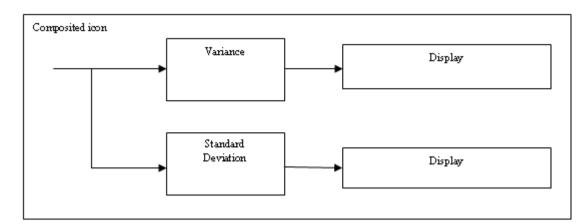

Post-processing block-set- For finding tumor here we use variance and standard deviation method. In this evaluate the variance and standard deviation of neighborhood element, presence of these original pixel value passed unchanged but tumor affected tissue will change the value, lockset as shown in figure 3.

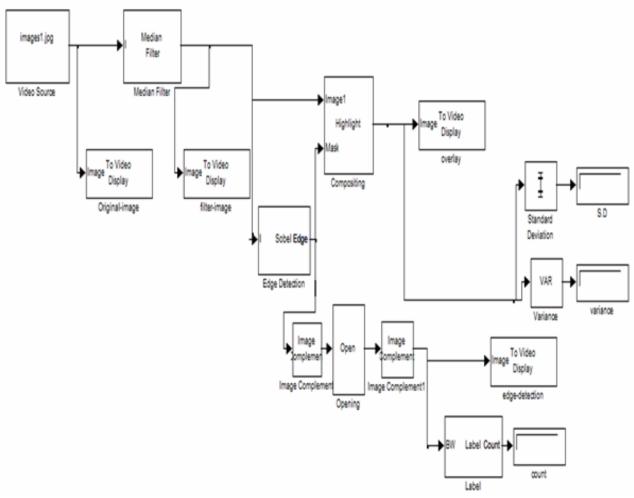

Whole implementation- By connecting all 3 stages of blockset full implementation of the process achieved.

As shown in figure 4. Here we use sobel as operator; other operator can be use in the place of sobel with the same block set. **Hardware Implementation**

For hardware implementation of this, image edge detection using Xilinx system generator. XSG created whole model and generate HDL code which can be synthesized in Xilinx FPGA. Design entry is the first step for FPGA design flow. The design entry of XSG based FPGA implementation is block diagram representation of entire system .Edge detection algorithm such as sobel, prewitt, robert, canny can be implemented using XSG.

Figure-2 Edge detection block-set

Figure-3 Post processing block-set

Figure-4 Whole block-set

| REAL IMAGE             | FILTERED IMAGE         | EDGE<br>DETECTION      | OVERLAY                |

|------------------------|------------------------|------------------------|------------------------|

| Artificial Brain image | Artificial Brain image | Artificial Brain image | Artificial Brain image |

|                        |                        |                        |                        |

| Normal brain Image     | Normal brain Image     | Normal brain Image     | Normal brain Image     |

|                        |                        |                        |                        |

| Abnormal brain image   | Abnormal brain image   | Abnormal brain image   | Abnormal brain image   |

|                        | Figure-5 Experi        |                        |                        |

Result

**Figure-5 Experiments Results**

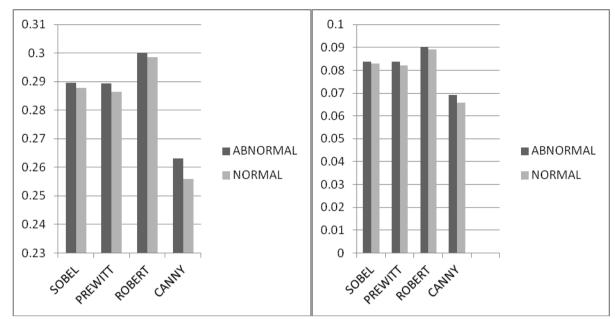

Figure-5 Standard deviation

**Figure-6 Variance**

### Table-1 Matrix value of different Ist order operator

| Operator | Gx                                                    | Gy                                                                        |

|----------|-------------------------------------------------------|---------------------------------------------------------------------------|

| Sobel    | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                     |

| Robert   | 1 0<br>0 -1                                           | 0 1<br>-1 1                                                               |

| Prewitt  | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{rrrrr} -1 & 0 & 1 \\ -1 & 0 & 1 \\ -1 & 0 & 1 \end{array}$ |

### Table-2 Matrix value of IInd order operator

| Operator                     | Gx                                                   |

|------------------------------|------------------------------------------------------|

| Laplacian of Gaussians (LOG) | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| Table -3 Result |                 |                    |          |  |

|-----------------|-----------------|--------------------|----------|--|

|                 | OPERATORS&CASES | STANDARD-DEVIATION | VARIANCE |  |

| 1               | SOBEL           |                    |          |  |

|                 | abnormal        | 0.2896             | 0.08386  |  |

|                 | normal          | 0.2879             | 0.0829   |  |

| 2               | CANNY           | 0.263              | 0.06915  |  |

|                 | abnormal        |                    |          |  |

|                 | normal          | 0.256              | 0.06574  |  |

| 3               | PREWITT         | 0.2893             | 0.08368  |  |

|                 | abnormal        |                    |          |  |

|                 | normal          | 0.2865             | 0.08209  |  |

| 4               | ROBERT          | 0.3002             | 0.09013  |  |

|                 | abnormal        |                    |          |  |

|                 | normal          | 0.2985             | 0.08912  |  |

|                 |                 |                    |          |  |

XILINX SYSTEM GENERATOR directly moves into bit stream file (\*.bit) from SIMULINK environment. Many component block diagram are available in SIMULINK library as well as their virtual input and output. SIMULINK supports UNIX and WINDOW environment. XILINX SYSTEM GENERATOR is high level tool for DSP system using FPGA. SYSTEM GENERATOR extension of SIMULINK mapped architecture, entities, sign, ports and attributes script file to produce synthesis in FPGA. The tool retains the hierarchy of SIMULINK when it is converted in to VHDL/Verilog. After this process it will co-simulated by JTAG co-simulator and implement on SPARTAN - 3E starter kit [1].

There are many research works related to image processing and its real time implementation using XSG which uses high end hardware similar to the one used in paper [3] by Sami Hasan, Alex Yakovlev and Said Boussakta *et al*, complicated design used in paper [4] by Zhang Shanshan *et al*, but the proposed design in this work eliminates the design complexity, takes least resource usage and also implemented in low cost basic FPGA device (Spartan 3E) [1]

### Conclusion

This paper proposed an idea of finding that the baby has tumor or not in his brain before birth which become new milestone in medical imaging field. Here Xilinx System Generator tool is a new application in image processing related work, and offers a block based design for processing. It also offers an ease of designing with GUI environment. This tool support software simulation, but most importantly it generates necessary files for implementation in all Xilinx FPGAs, with the parallelism, robust, speed and automatic area minimization. These features are mandatory in real time image processing. The design architecture used in this paper can be used for all Xilinx FPGA Kit with proper user configuration in System generator block and could be extended to real time image processing [1].

### References

[1]Mrs. S. Allin Christe1, Mr.M.Vignesh2, Dr.A.Kandaswamy, "AN Efficient FPGA Implementation of MRI Image FIltering and Tumour Characterization using Xilinx System Generator", International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.4, December 2011.

[2]C.Sujatha and D Selvathi,"Hardware Implementation of Image Edge Detection Using Xilinx System Generator",Asian journal of Scientific Research,2014

[3] Sami Hasan, Alex Yakovlev and Said Boussakta, "Performance Efficient FPGA Implementation of Parallel 2-D MRI Image Filtering Algorithms using Xilinx System Generator", CSNDSP IEEE, 2010

[4] ZhangShanshan and WangXiaohong," Vehicle Image Edge Detection Algorithm Hardware Implementation on FPGA", International Conference on Computer Application and System Modeling, ICCASM 2010.

[5] Anthony Edward Nelson," Implementation of Image Processing Algorithms on FPGA hardware", MS thesis, May 2000.

[6] C. John Moses, Dr. D. Selvathi, S.Sajitha Rani, "FPGA Implementation of an Efficient Partial Volume Interpolation for Medical Image Registration", ICCCCT-10, 2010 IEEE

[7] Robert D. Turney, Chris Dick1, David B.Parlour, and James Hwang, "Modeling and Implementation of DSP FPGA Solutions", Xilinx Inc.

[8] Yu-Min Lee, "Introduction to VLSI Design".

[9] Gonzales," Digital Image processing", 3<sup>rd</sup> edition.

[10] Sang Chul Ahn," Digital Image Processing", UST Fall 2007.

[11] Ahmed Elhossini, "Using Xilinx System Generator 13.2 for Co-Simulation on Digilent NEXYS3 (Spartan-6) Board", February 22, 2013.