Behzad Ghanavati/ Elixir Elec. Engg. 88 (2015) 36501-36504

Awakening to reality Available online at www.elixirpublishers.com (Elixir International Journal)

# **Electrical Engineering**

Elixir Elec. Engg. 88 (2015) 36501-36504

# A Low voltage CMOS Fuzzifier Using Adaptive Biasing

Behzad Ghanavati

Department of Electrical Engineering, Mahshahr Branch, Islamic Azad University, Mahshahr, Iran.

## **ARTICLE INFO**

Article history: Received: 20 June 2012; Received in revised form: 15 November 2015; Accepted: 20 November 2015;

## ABSTRACT

A versatile low-voltage CMOS Fuzzifier circuit with a trapezoidal transconductance characteristic and independently programmable slope, height and horizontal position is designed in  $0.35\mu$  m standard CMOS technology. The proposed circuit uses adaptive biasing linearization techniques to achieve wide tuning range. Simulation results using HSPICE and level 49 parameters (BSIM3v3) that verify the functionality of circuit with 1.5 V supply are presented.

© 2015 Elixir All rights reserved.

## Keywords

Fuzzifier, Transconductor, Low-voltage, Low-power, Adaptive Biasing, Fuzzy.

#### Introduction

Zadeh proposed in 1965 a logic with fuzzy truth, connection and rules of inference, which was named Fuzzy logic. This approach has been successfully applied in many fields, like automatic process control and expert system and pattern recognition.

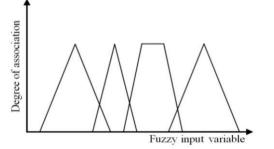

The fundamental operation in fuzzy logic is fuzzification which consists of the determination of the degree of association of a variable to a fuzzy set [1] and is implemented by means of fuzzifier. This circuit provides a nonlinear relation that measures the compatibility of an object with the concept represented by a fuzzy set. Usually, fuzzifiers have a triangular or trapezoidal shape and, in order to guarantee general application, it needs to have programmable parameters (horizontal position, height, width and edge slope). [2] (Fig.1)

# Fig 1. Fuzzification of an input variable using membership function

For designing Fuzzifiers three generally methods exist; voltage-mode, current-mode and transconductance-mode B. Ghanavati is with the Department of Electrical Engineering, Islamic Azad University, Mahshahr Branch, Mahshahr, Iran (e-mail: B.ghanavati@mahshahriau.ac.ir).circuits. Input and output signals are voltages in voltage-mode circuits and currents in current-mode circuits.

Transconductance-mode circuits have a voltage input signal and a current output signal. This latter choice is often preferred as the distribution of the input signals and the combination of the output Signals are simplified. Using these techniques several interesting CMOS fuzzifier have been reported. [3]- [7] Often in the applications which fuzzifier in transconductance mode is used, the input transconductor determine the overall linearity of the system. Modern fabrication technologies and wireless applications also require low supply voltage and low power consumption, which make it difficult to achieve transconductors with high linearity and low supply voltage over a reasonable input range.

Consequently, multiple circuit techniques have been proposed in literature to improve the linearity of MOS transconductors.[8]- [11] The reported linearization techniques include: cross-coupling of multiple differential pairs, adaptive biasing, source degeneration (using resistor or MOS transistor), shift level biasing, series connection of multiple differential pairs and pseudo-differential stages(using transistor in the triode region or in saturation).

In this paper, we report a versatile circuit for the implementation of CMOS transconductance-mode fuzzifier circuit. The circuit uses supply voltages 1.5V which significantly lower than most previous proposals. The circuit uses the adaptive biasing techniques to improve the linearity.

Furthermore, it can be employed for all applications where a highly accurate voltage to current conversion should be realized. The adaptive biasing linearization technique has been briefly reviewed in section 2 and the proposed high-linear MOS transconductor is introduced in this section, also the dc transconductance characteristic of the proposed circuit is presented in this Section.

The proposed fuzzifier is presented in section 3 and several simulation results are presented in section 4. Conclusion is presented in section 5.

#### **CMOS Implementation of Fuzzifier circuit**

In this section, a new circuit for the generation of trapezoidal functions is described. In the following, the proposed circuit will be presented starting from the linear transconductor used. Then the circuitry needed to generate the trapezoidal shapes will be added.

#### Linear Transconductor Design

Considering quadratic i - v characteristics for the MOS transistors and neglecting the channel length modulation effect, the simple differential MOS transconductor has a transfer characteristic given by

$$\mathbf{i_o} = \sqrt{2KI_o} \mathbf{v_i} \sqrt{1 - \frac{\mathbf{v_i}^2 \mathbf{K}}{8I_o}}$$

(1)

Where k represents the transconductance parameter

Where k represents the transconductance parameter  $\binom{k}{L} = \mu C_{ox} \frac{W}{L}$ .

Better linearity can be achieved for large effective gate-tosource voltages  $V_{GSeff} = V_{GS} - V_{TH}$ . For low-voltage applications this constitutes a major drawback Furthermore, large transconductance values can be obtained only by using large bias currents and large area transistors; however this changes cause to enlarge the power consumption and active area.

One of the topologies for linearization of the transfer characteristic of MOS transconductors is using the adaptive biasing current source.[12]

The idea is using a dynamic bias current containing an input dependent quadratic component to cancel the nonlinear term in equation (1). Hence, if the bias is defined as equation (2),

$$I_o = I'_o + \frac{kv_i^2}{8} \tag{2}$$

And put this equation in equation (1) the transfer characteristic becomes linear and could be realized according to equation (3)

$$i_o = \sqrt{2kl'_o v_i} \tag{3}$$

B. The novel low-voltage circuit for generating the adaptive bias current

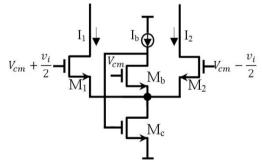

Fig. 2 shows the new low-voltage circuit for generating the adaptive bias current.

Fig. 2 Adaptive bias current generator

Assuming the same sizes for M<sub>1</sub>, M<sub>2</sub>, it can be easily shown that:

$$l_{1} = \frac{1}{2}k_{1}\left(V_{cm} + \frac{v_{i}}{2} - V_{cm} + V_{GSb} - V_{th}\right)^{2} = \frac{1}{2}k_{1}\left(\frac{v_{i}}{2} + V_{GSb} - V_{thb}\right)^{2}$$

Where  $k_1$  is the transconductance parameter of input devices,  $M_1$

(4)

$$k_{1} = k_{2} = \mu C_{ox} \frac{W_{1}}{L_{1}}$$

Similar attempt for  $I_2$  terminates to equation (5):

$$I_{2} = \frac{1}{2}k_{2}\left(\frac{-v_{i}}{2} + V_{GSb} - V_{th}\right)^{2}$$

(5)

Replacing  $V_{GSb}$  as a function of the bias current  $I_b$

$$V_{GSb} = V_{th} + \sqrt{\frac{2I_b}{\mu C_{ox} \frac{W_b}{L_b}}}$$

(6)

The following expression result:

$$I_{1} = \frac{1}{2}k_{1}\left(\frac{v_{i}}{2} + \sqrt{\frac{2I_{b}}{\mu C_{ox}\frac{W_{b}}{L_{b}}}}\right)^{2}$$

$$I_{2} = \frac{1}{2}k_{2}\left(\frac{-v_{i}}{2} + \sqrt{\frac{2I_{b}}{\mu C_{ox}\frac{W_{b}}{L_{b}}}}\right)^{2}$$

$$(7)$$

$$(8)$$

The current passing through  $M_C$  is equal to the sum of  $I_1$ ,  $I_2$  and  $I_b$  as clarified in equation (9):

$$I_{c} = I_{1} + I_{2} + I_{b} = I_{b} + \frac{1}{2}k_{1}\left(\frac{v_{i}^{2}}{2} + \frac{4I_{b}}{\mu C_{ox}\frac{W_{b}}{L_{b}}}\right)$$

(9)

As seen in (9), the current of  $M_C$  is related in quadratic relation with the input differential voltage.

If a copy of the current of  $M_C$  is mirrored into the tail current of basic differential pair which is discussed former in section 2.1, equation (10) can be concluded from combination of equations (1) and (9):

$$i_{o} = \frac{1}{2}kv_{i}\sqrt{\frac{8}{k}}l_{b} + \frac{16k_{1}}{kk_{b}}l_{b} + \frac{2k_{1}}{k}v_{i}^{2} - v_{i}^{2}$$

(10)

Where

$$k = \mu C_{ox} \frac{W}{L}$$

is the transconductance of basic

differential pair,  $k_{1} = \mu C_{ox} \frac{W_{1}}{L_{1}}$  is the transconductance of  $W_{1}$

adaptive biasing differential pair and  $k_b = \mu C_{ox} \frac{w_b}{L_b}$  is the transconductance of  $\mathbf{M}_b$  transistor. If  $k_1 = 0.5k$  the transfer characteristic becomes completely linear according to relation (11):

$$i_o = \frac{1}{2}kv_i \sqrt{\frac{8}{k}I_b + \frac{8}{k_b}I_b}$$

(11)

#### The novel linear MOS transconductor

\_ . . .

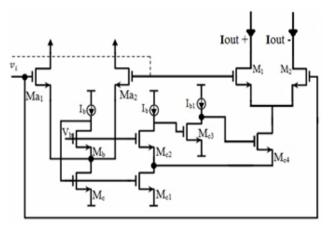

We proposed a new MOS transconductor that uses the linearization approach presented above. The proposed circuit consists of 3 main blocks; an adaptive biasing current generator, a high performance current mirror and a main differential pair (fig. 3).  $M_{C1}$ -  $M_{C4}$  Formed a high performance current mirror. [13] This circuit copy the dynamic current that produced by Adaptive bias current generator circuit which formed by  $M_{a_1}$ ,  $M_{a_2}$ ,  $M_b$  and  $M_c$  into the source of the transistors of main differential pair with source degeneration transistor which formed by  $M_1$ -  $M_2$ .

Fig. 3. The novel linear transconductor

$M_b$ , current source  $I_b$  and  $V_b$  forces the  $V_{DS}$  voltage of transistor  $M_C$  to a constant value. A replica of this circuit is used to force the  $V_{DS}$  voltage of the transistor  $M_{C1}$  to be equal to that of transistor  $M_C$ .

To have high output impedance, the output cascade transistor  $M_{C4}$  is driven by the drain of transistor  $M_{C2}$ . As the polarity in the drain of transistor  $M_{C2}$  is reversed, an inverting stage is required to drive the gates of transistor  $M_{C4}$ . This Inverting stage provides additional gain-boosting, which increases the output impedance. The inverter amplifier has been implemented by means of transistor  $M_{C3}$  and biasing current  $I_{b1}$ . The minimum supply voltage is limited by the path formed by  $I_b$ ,  $M_b$  and  $M_{C}$ , so the minimum supply voltage is

$\mathbf{V}_{\text{DD}}^{\min} = \mathbf{V}_{GSC} + 2\mathbf{V}_{DSbsat} \tag{12}$

where  $V_{GSC}$  is gate-source voltage of  $M_C$ ,  $V_{DSbsat}$  is the minimum voltage drop in current source  $I_b$  and can be as small as 0.15V in 0.35µm CMOS technology,  $V_{th} = 0.65$  V for NMOS ,so

$V_{DD}^{min} = V_{th} + 3V_{DSsat} = 0.65 + 3 \times 0.15 = 1.1$  V

We have selected  $V_{DD}$ =1.5 V in order to have an appreciable voltage swing.

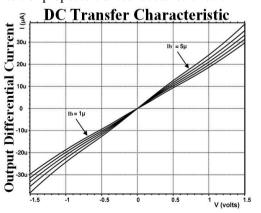

The proposed transconductor was laid out in standard  $0.35\mu m$  CMOS technology. Post layout simulations from extracted circuit were performed for a single 1.5 V supply using HSPICE and level 49 parameters (BSIM3V3). Fig. 4 shows DC characteristic of proposed transconductance circuit.

Fig. 4. .Post layout simulated DC transfer characteristic for Ib from 1µA to 5µA by 1µA step

#### **Fuzzifier circuit**

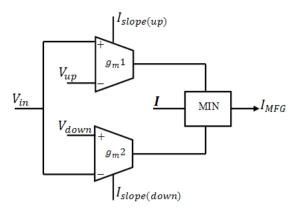

Using two instances of transconductor in Fig.4 and a minimum current selector circuit, a trapezoidal transconductor characteristic can be generated (Fig.5)

Fig.5 (a) MFG block diagram (b) MFG output

This block consists of two transconductors. One creates a positive ramp and the other creates a negative ramp, one defines the  $V_{up}$  and the other defines  $V_{down}$ , also each transconductor can independently define the slope of the up and down part via bias current  $I_b$ , then outputs go through a minimum current selector circuit which takes the minimum of them to construct a trapezoid output current.

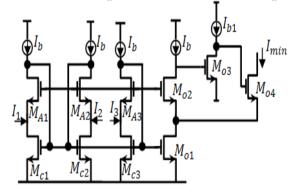

The new low voltage MIN circuit is shown in Fig.6

#### Fig 6. MIN circuit

A proposed circuit has 3 input branches and each branch consists of a current sensing transistor  $M_{\rm Ci}$  and a voltage follower  $M_{\rm Ai}$  while the gates of transistors  $M_{\rm Ai}$  are connected to a common-mode constant voltage  $V_b$ .

$V_{GS}$  voltages of all  $M_{Ci}$  transistors are equal and proportional to minimum of input currents of  $I_1$ ,  $I_2$ ,  $I_3$ .this condition drive them to have different  $V_{DS}$  voltage. Since they  $(M_{C1}, M_{C2} \text{ and } M_{C3})$  have different  $V_{DS}$  voltage, the voltage follower of all branches  $(M_{A1}, M_{A2} \text{ and } M_{A3})$  are turned off with the exception of voltage follower in the loosing branch that has the minimum of input currents  $I_1$ ,  $I_2$  and  $I_3$ .

This transistor remains ON and with  $M_{O1}$ -  $M_{O4}$  formed a high performance current mirror that can copy the minimum current to the output.

This MIN circuit also defines the fuzzy one level for whole MFG circuit. By choosing the value of  $\mathbf{I}$  for the fuzzy one value we also can cut the output signal at the level we want so in other words selecting  $\mathbf{I}$  value, we can use the most linear part of the output signal.

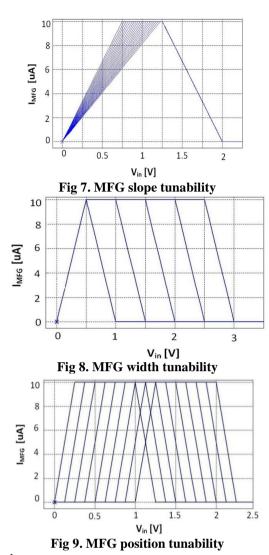

## Simulation

The Fuzzifier depicted in fig.6 was laid out in standard 0.35µm CMOS technology. Post layout simulations from extracted circuit were performed for a single 1.5 V power supply voltage using HSPICE and level 49 parameters (BSIM3V3).

Figure 7 and 8 and 9 shows SPICE simulation of the MFG. All the parameters are independently tunable.

#### Conclusion

A novel low-voltage CMOS circuit for the Implementation of trapezoidal transconductance Functions with programmable characteristics have been introduced. The proposed circuit uses the source degeneration linearization method to achieve better linearity. The circuit can be used for the implementation of VLSI analogue neuro-fuzzy systems. The proposed circuit has independently adjustable height, slope, position, and width of the trapezoidal function and has been verified by simulation results.

#### REFERENCES

[1] L.A. Zadeh, "Fuzzy sets", Inf. Contr., Vol. 8, pp.338-353, 1965.

[2] M. Sasaki, N. Ishikawa, F. Ueno, and T. Inoue, "Currentmode analogue fuzzy hardware with voltage input interface and normalization locked Loop," IEICE Trans. Fund., vol. E75-A, no. 6, pp. 650–654, Jun. 1992.

[3] A. Thomsen and M. A. Brooke, "A programmable piecewise-linear Large-signal CMOS amplifier", IEEE J. Solid-State Circuits, vol. 28, no.1, pp. 84–89, Jan. 1993

[4] J. Van Valburg and R. J. van de Plassche, "An 8-bit 650-MHz folding ADC," IEEE J. Solid-State Circuits, vol. 27, no. 12, pp. 1662–1666, Dec.1992.

[5] Amin Khalilzadegan, Abdollah Khoei and Khayrollah Hadidi "Circuit implementation of a fully programmable and continuously slope tunable triangular/trapezoidal membership function generator", Analog Integrated Circuits and Signal Processing, Online First<sup>TM</sup>, 18 August 2011

[6] Ali Naderi, Abdollah Khoei and Khayrollah Hadidi "Circuit implementation of high-resolution rational-powered membership functions in standard CMOS technology", Analog Integrated Circuits and Signal Processing, 2010, Volume 65, Number 2, Pages 217-223

[7] M.Kachare, J. Ramirez-Angulo, R.G. Carvajal, A. Lopez-Martin, "New Low-Voltage Fully Programmable CMOS Triangular/Trapezoidal Function Generator Circuit" IEEE Trans. Circuits and Systems-I:REGULAR PAPER, Vol.52, No. 10, pp.2033-2042, Oct. 2005.

[8] A.Worapishet and C.Nephaphan, "Current-feedback sourcedegenerated CMOS transconductor with very high linearity", Electronics Letters, Volume 39, Issue 1, No.1, Jan 9, 2003

[9] M.Kachare, A. Lopez-Martin, J. Ramirez-Angulo, R.G. Carvajal, "A Compact Tunable CMOS Transconductor with High Linearity" IEEE Trans. Circuits and Systems-II:EXPERESS BRIEFS, Vol.52, No. 2, pp.82-84, Feb. 2005.

[10] Ko-Chi Kuo and Adrian Leuciuc, "A Linear MOS Transconductor Using Source Degeneration and Adaptive Biasing" IEEE Trans. Circuits and Systems-II:ANALOGUE AND DIGITAL SIGNAL PROCESSING, Vol.48, No. 10, pp.937-943, Oct. 2001.

[11] F. Krummenacher and N. Joehl, "A 4-MHz CMOS Continuous-Time Filter with On-Chip Automatic Tuning," IEEE J. of Solid-State, Vo1.23, pp.750-758, June 1988.

[12] A. Nedungadi and T. R. Viswanathan, "Design of Linear CMOS transconductance elements," IEEE Trans. Circuits and Systems, Vol. CAS-31, No. 10, pp.891-894, Oct. 1984.

[13] J. Ramirez-Angulo, M.S.Sawant, , A. Lopez-Martin, R.G. Carvajal, "Compact Implementation of High Performance CMOS current mirror", Electronics Letters, Volume 41, Issue 10, May 12, 2005 Page(s):3 – 4